THE WAR

# TD674OAN/AF

#### T-51-09-05

#### 14-BITS LOW POWER D/A CONVERTER

TD6710AN/AF is dual-slope single-integral 14-bits low-power D/A converter, designed for use in PCM digital audio equipments.

- . Corresponding with 2's complement code.

- Reduced number of external components by means of built-in sample hold circuit.

- . Corresponding with sampling frequency  $44.1 \mathrm{kHz}$ .

- Alternate D/A conversion of both signals of right and left stereo channels.

- . +5V single power supply.

- . Low power dissipation. ( $P_D=100mW\ TYP.$ )

- . S/N ratio : 83.5dB TYP.

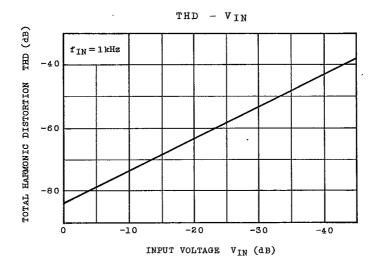

THD

: 0.008% TYP.

(Without aperture compensation)

#### MAXIMUM RATINGS (Ta=25°C)

| <u> </u>              |                  |         |                                                 |    |  |

|-----------------------|------------------|---------|-------------------------------------------------|----|--|

| CHARACTERIS           | SYMBOL           | RATING  | UNIT                                            |    |  |

| Analog Supply Volt    | V <sub>CCA</sub> | -0.3~8  | V                                               |    |  |

| Digital Supply Vol    | $v_{CCD}$        | -0.3~8  | V                                               |    |  |

| Input Voltage         |                  | VIN     | GND <sub>D</sub> -0.3<br>~V <sub>CCD</sub> +0.3 | V  |  |

| Power Dissipation     | TD6710AN         | $P_{D}$ | 1300                                            | mW |  |

|                       | TD6710AF         | עב      | 400                                             |    |  |

| Operating Temperature |                  | Topr    | -25~75                                          | °C |  |

| Storage Temperature   |                  | Tstg    | -55~150                                         | °C |  |

T-51-09-05

## TD6710AN/AF

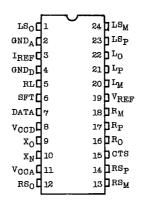

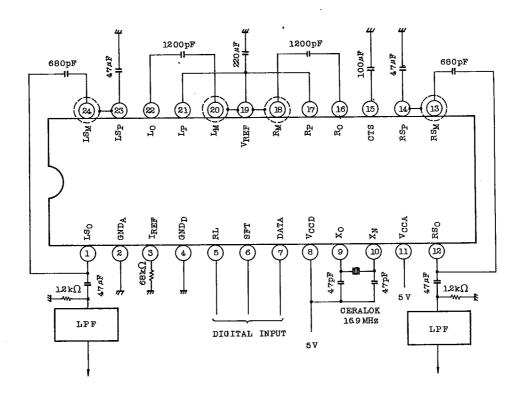

PIN CONNECTIONS

1.30 1.40 3

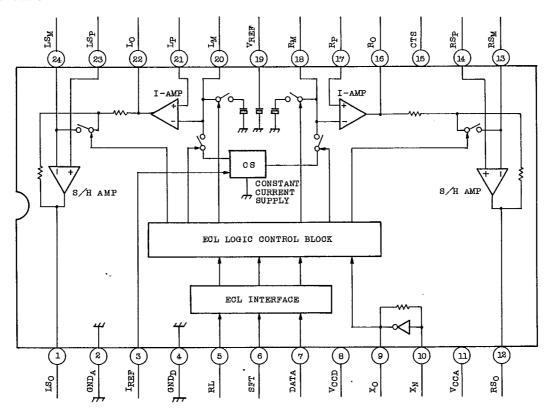

BLOCK DIAGRAM

T-51-09-05

#### ELECTRICAL CHARACTERISTICS (Unless otherwise specified, Ta=25°C, V<sub>CCA</sub>=V<sub>CCD</sub>=5V)

| CHARAGTERISTIC                 |           | SYMBOL            | TEST<br>CIR-<br>CUIT   | TEST CONDITION                                   | MIN. | TYP. | MAX. | UNIT |  |

|--------------------------------|-----------|-------------------|------------------------|--------------------------------------------------|------|------|------|------|--|

| Operating Supply Voltage       |           | v <sub>cca</sub>  |                        |                                                  | 4.5  | 5    | 8    | v    |  |

|                                |           | $v_{CCD}$         |                        |                                                  | 4.5  | 5    | 8    | 3    |  |

| Operating Supply Current       |           | ICCA              | 1                      | At non-signal                                    | 7.0  | 10.0 | 13.0 | mA   |  |

|                                | •         | ICCD              | 1                      |                                                  | 6.4  | 8.5  | 10.6 |      |  |

| Input Voltage                  | "H" Level | $v_{\mathrm{IH}}$ | -                      | RL, SFT, DATA terminal                           | 2.9  | -    | -    | v    |  |

|                                | "L" Level | $v_{IL}$          | -                      | 11                                               | -    | -    | 1.4  |      |  |

| Input Current                  | "H" Level | IIH               | -                      | " V <sub>IH</sub> =5V                            | -    | -    | 4    | μА   |  |

|                                | "L" Level | $I_{IL}$          | -                      | v <sub>IL</sub> =0v                              | -    | 1    | 1    |      |  |

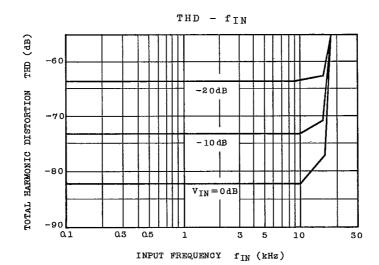

| Total Harmonic<br>Distortion   |           | THD               | 1                      | OdB (full-scale) input                           | _    | -82  | -80  | dB   |  |

| SN Ratio                       |           | s/n               | 1                      | Value of -20dB input,<br>added by +20dB          | 82   | 83.5 | -    | dВ   |  |

| Cross-Talk                     |           | С.Т               | 1                      | Single channel OdB<br>(full-scale) input         | 81   | 83   | -    | dB   |  |

| Output Voltage                 |           | VRSO              | 1                      | OdB (full-scale) input                           | -3   | -2   | _    | dBV  |  |

|                                |           | VLSO              | oub (luli-scale) imput |                                                  |      | _    |      | ""   |  |

| Output Differential<br>Voltage |           | v <sub>od</sub>   |                        | OdB (full-scale) input $V_{\rm RSO}-V_{\rm LSO}$ | -0.6 | 0    | 0.6  | dBV  |  |

| Built-in Reference<br>Voltage  |           | $v_{REF}$         | _                      |                                                  | 2.2  | 2.3  | 2.4  | V    |  |

| S/H AMP<br>Reference Voltage   |           | VRSP              | _                      |                                                  | 2.4  | 2,5  | 2.6  | V    |  |

|                                |           | $v_{LSP}$         | ]                      |                                                  |      |      |      |      |  |

| Operation Frequency            |           | fop               | -                      |                                                  | 16.5 | 16.9 | 20   | MHz  |  |

TEST CIRCUIT 1: Application circuit is used, and RL, SFT, DATA, analog output are as follows.

- .  $f_{RL}=44.1kHz$

- .  $f_{SFT}=1.4112MHz$

- . DATA : f=1kHz

- . Analog output : -3dBV at 0dB input

#### FUNCTION OF EACH PIN

| PIN No. | SYMBOL                      | FUNCTION DESCRIPTION                                                                                                                                                                                             | REMARKS                                                                                                      |

|---------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 1       | LSO                         | Lch sample hold output terminal.                                                                                                                                                                                 | •                                                                                                            |

| 2       | GNDA                        | Analog GND terminal.                                                                                                                                                                                             |                                                                                                              |

| 3       | ${ m I}_{ m REF}$           | Reference current input terminal. Input for determining current of constant current supply. Connect the resistor ( $68k\Omega$ ) between this terminal and GNDA.                                                 |                                                                                                              |

| 4       | $\mathtt{GND}_{\mathbf{D}}$ | Digital GND terminal.                                                                                                                                                                                            |                                                                                                              |

| 5       | RL                          | Input data L,Rch indication signal input terminal. Used as control signal in LSI. Requested to be input in synchronization with SFT trailing edge. $f_{RL}$ =44.1kHz duty cycle=50%                              |                                                                                                              |

| 6       | SFT                         | Shift clock input terminal.  Clock for reading bit-serially PCM digital audio 16-bit data into LSI from MSB side.  f <sub>SFT</sub> =1.4112MHz, duty cycle=50%                                                   |                                                                                                              |

| 7       | DATA                        | PCM digital audio data input terminal.  Requested to be input bit-serially (each 16-bit data) from MSB side in synchronization with SFT trailing edge.  Corresponding to RL signal "L" level=Lch, "H" level=Rch. |                                                                                                              |

| 8       | $v_{CCD}$                   | Digital power supply voltage terminal. +5V                                                                                                                                                                       |                                                                                                              |

| 9       | x <sub>O</sub>              | Input terminal for oscillation circuit.  Modified colpitts oscillation circuit is constructed through the combination of X'tal oscillation terminal with C.                                                      | Ceralok is applicable.  16.9MHz can be supplied to XN from outside.  (upto CMOS level).  Connect XO to VCCD. |

| - 11    | V <sub>CCA</sub>            | Analog power supply voltage terminal. +5V                                                                                                                                                                        |                                                                                                              |

T-51-09-05

| PIN No. | SYMBOL           | FUNCTION DESCRIPTION                                                                                                                                                | REMARKS |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 12      | RS <sub>O</sub>  | Rch sample.hold output terminal.                                                                                                                                    | ·       |

| 13      | RSM              | Negative input terminal for Rch sample hold ope-amp. Hold capacitor is connected to RSO and RSM.                                                                    |         |

| 14      | RSp              | Positive input terminal for Rch sample hold ope-amp.                                                                                                                |         |

| 15      | CST              | Internal constant current supply terminal.  De-coupling capacitor is connected to ground.                                                                           |         |

| 16      | RO               | Rch integrator output terminal.                                                                                                                                     |         |

| 17      | Rp               | Positive input terminal for Rch integrator ope-amp.                                                                                                                 |         |

| 18      | RM               | Negative input terminal for Rch integrator ope-amp. Integrating capacitor is connected to $R_{\rm O}$ and $R_{\rm M}$ .                                             |         |

| 19      | V <sub>REF</sub> | Integrator reference power supply voltage terminal. Power supply is constructed inside LSI and is connected to positive inputs LP,Rp for L, Rch integrator ope-amp. |         |

| 20      | L <sub>M</sub>   | Negative input terminal for Lch integrator ope-amp. Integrating capacitor is connected to LO and LM.                                                                |         |

| 21      | Lp               | Positive input terminal for Lch integrator ope-amp.                                                                                                                 |         |

| 22      | LO               | Lch integrator output terminal.                                                                                                                                     |         |

| 23      | LSP              | Positive input terminal for Lch sample hold ope-amp.                                                                                                                |         |

| 24      | LSM              | Negative input terminal for Lch sample hold ope-amp.  Hold capacitor is connected to LSO and LSN.                                                                   |         |

#### DESCRIPTION ON OPERATION OF EACH BLOCK

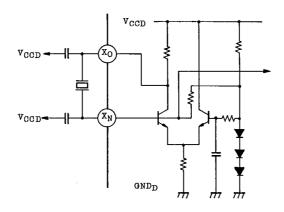

#### 1. OSCILLATION CIRCUIT

Modified colpitts oscillator can be constructed with internal amplifier by connecting external X'tal (or ceralok) and capacitor.

The oscillation output is input to the control block and is used as the clock pulse for determining the intergration period.

Fig. 1 EXAMPLE FOR APPLICATION OF X'tal CERALOK OSCILLATOR

#### 2. CONTROL BLOCK (ECL LOGIC)

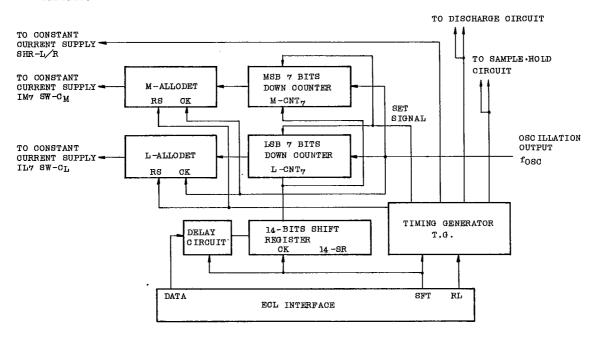

Control block is constructed with the following four blocks as shown in Fig. 2.

(1) 14-bits shift register

: 14-SR

(2) 7-bits preset type downcounter: M-CNT7 and L-CNT7

(3) ALL 0 detection circuit

: M-ALLO DET and L-ALLO DET

(4) Timing generator

: T.G.

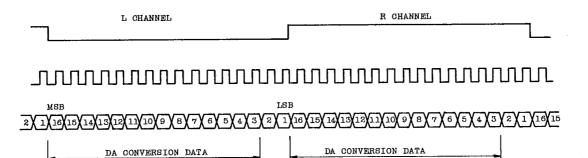

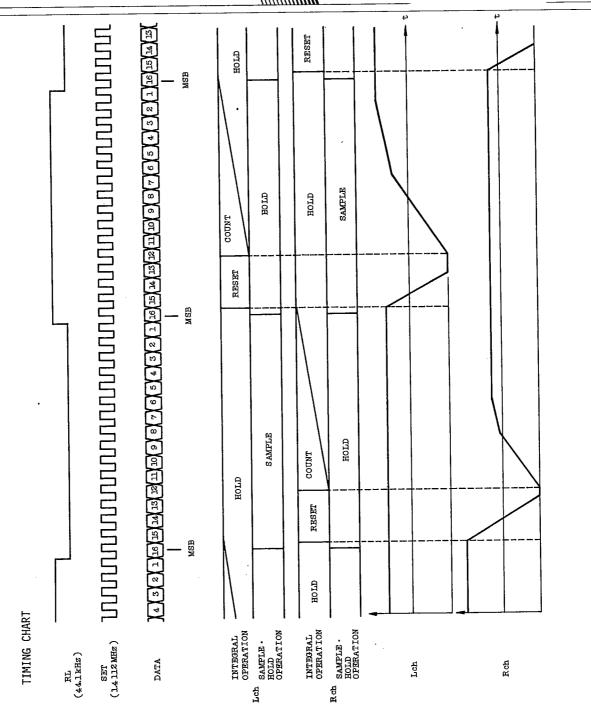

Each signal of RL, SFT and DATA is input to ECL logic interface and DATA is loaded on 14-bits shift register 14SR through the DELAY circuit at SFT leading

The loaded data performs DA conversion of the data, which is set to 14-SR, by means of carrying out the counting and the integrating operations at the same time through using the oscillation output fosc.

T-51-09-05

Finally, this DA converted output is output outside through the samples hold circuit.

Fig. 2 CONTROL BLOCK CONFIGURATION

Description is made on each block in the following.

(1) 14-bits shift register: 14-SR

Each 16-bits of L and R stereo channel digital audio data is loaded on 14-SR at the leading edge of SFT in order from the most significant bit (MSB) side.

When 16 bits of L or R channel are loaded completely, the 14 bits data are devided into MSB side 7 bits and LSB side 7 bits to be in dividually set to the down counters M-CNT7 and L-CNT7. (To 14-SR, 14 bits of before the leading and the trailing edges of RL signal.)

A TOP

Fig. 3 EACH INPUT SIGNAL TIMING CHART OF RL, SFT AND DATA

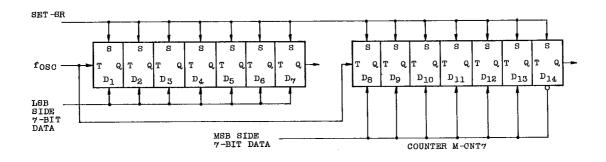

(2) Down Counter: M-CNT7, L-CNT7

As soon as the data is set to M-CNT7 and L-CNT7, each counter starts its down-count operation.

Because the input of 14-bits digital audio signal is 2'S complementary code, MSB data D14 of M-CNT7 is inverted and input.

Fig. 4 CONFIGURATION OF COUNTER M-CNT7 AND L-CNT7

DE

### TD6710AN/AF

T-51-09-05

- (3) ALLO detection circuit of counter: M-ALLO DET, L-ALLO DET

As soon as the data is set to M-CNT7 and L-CNT7, M-ALLO DET and L-ALLO DET

are reset by the O-RS signal which is input from T.G. and the constant

current supply is connected to the integrating circuit.

The completion of the integrating operation is detected from the state

change of the outputs Q14 and Q7 of M-CNT7 and L-CNT7. After M-ALLO DET

and L-ALLO DET are set, the constant current supply unit is separated from

the integrating circuit.

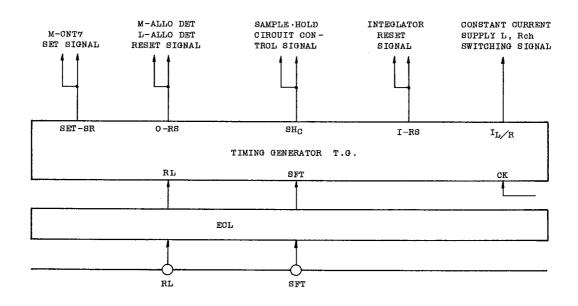

- (4) Timing Generator: T.G.

Through ECL interface circuit, input each signal RL and SFT to output the following signals to each unit.

- . Set signals for M-CNT7 and L-CNT7:

- . Reset signal for ALLO detection circuit:

- . Control signal for sample hold circuit:

- . Control signal for switching L and R channels of constant current supply:

- . Integrator reset signal:

Fig. 5 INPUT AND OUTPUT OF TIMING GENERATOR SIGNALS

DE

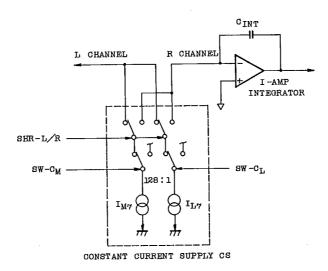

3. CONSTANT CURRENT SUPPLY CIRCUIT: CS128

The constant current supply unit is composed of two constant current supplies: IM7 for MSB side 7 bits, and IL7 for LSB side 7 bits. By means of designing the current ratio of IM7 and IL7 as 128:1, and using IM7 combined with the counter M-CNT7 and IL7 with the counter L-CNT7, the coefficient corresponding to the set data for the counter is converted into the integration period. The counting number 1 of MSB side counter M-CNT7 is made corresponded to the counting number 128 of LSB side counter-CNT7.

By using  $I_{M7}$  and  $I_{L7}$  at the same time, the following expression is obtained instead of the conventional single slope single integration system, and the alternative output of PCM digital audio 16-bits data (14-bits accuracy) is made possible in 44kHz with  $f_{OSC} \doteqdot 17 \text{MHz}$ .

Max. counting number ratio =

$$\frac{2^7}{216}$$

=  $\frac{1}{512}$

The constant current supplies  $I_{M7}$  and  $I_{L7}$  carry out ON/OFF of SW-CM and SW-CL with the control signal which is output from the counter all 0 detection circuits M-ALLO DET and L-ALLO DET of the control block in Fig. 2.

Fig. 6 CONFIGURATION OF CONSTANT CURRENT SUPPLY

T-51-09-05

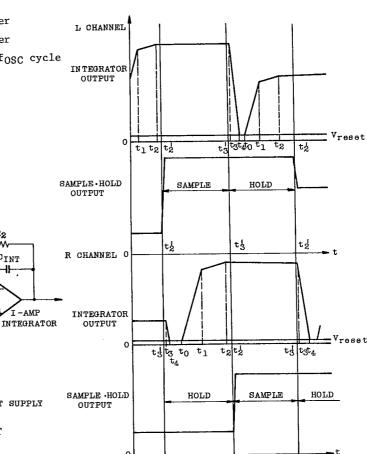

#### 4. INTEGRATION CIRCUIT

The integration circuit is composed of built-in ope.-amp. and external CINT. The period of to~t2 in Fig.8 is the period for charging to CINT by (integrating operation) the constant current supply  $I_{\mbox{\scriptsize M7}}$  and  $I_{\mbox{\scriptsize L7}}$  in the integration circuit in Fig.7 and for counting and voltage conversion (DA conversion).

The integration period is determined by either value of larger one stored in the counter M-CNT7 or L-CNT7 of the control block and is determined as follows.

$$v_{10} = \frac{1}{c_{INT}} \cdot (i_{M7} \cdot n_{M} + i_{L7} \cdot n_{L}) \cdot i_{OSC} + v_{reset}$$

$c_{INT}$

41-

CONSTANT CURRENT SUPPLY

I - AMP

Fig. 7 INTEGRATION CIRCUIT

RS-AMP

RESET

CIRCUIT

INTEGRATOR OUTPUT, SAMPLE. Fig. 8 HOLD OUTPUT VARIATION

tģ

ŀ

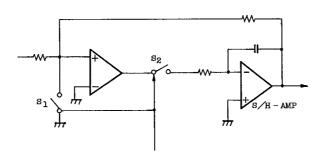

#### 5. SAMPLE · HOLD CIRCUIT

This circuit sample-holds the stabilized voltage during the period of  $t_2^1 - t_3^1$  and outputs the voltage outside. At  $t_2^1$ ,  $t_3^1$  is made OFF and  $t_3^1$  and  $t_3^1$  is made ON and  $t_3^1$  and the sampling voltage is hold.

Fig. 9 SAMPLE · HOLD CIRCUIT

#### 6. RESET CIRCUIT

During the period of  $t_3$ - $t_4$ ,  $S_r$  of the integration circuit in Fig.7 is made ON and the integration capacitor  $C_{\rm INT}$  is discharged.

Until the balanced state of  $V_{0(reset)}=V_r$  is obtained, discharge is carried out with the reset amplifier RS-AMP.

TOSHIBA, ELECTRONIC D2 DE 90'

9097247 0018788 7

## TD6710AN/AF

T-51-09-05

ij

EXAMPLE OF APPLICATION CIRCUIT

- Note 1. To improve characteristics, form the guard ring pattern for pins 13,18,20,24 as shown in the circuit above.

- 2. Use polystyrol capacitor (precision: within  $\pm 3\%$ ) for integrated capacitor.

- 3. Connect the capacitor to VCCA-GNDA and VCCD-GNDD against high frequency noise. Capacitor is  $0.0039\mu F$  or so.

- 4. External constant is the standard value.

20.80414.5

# TD6710AN/AF

T-51-09-05

Graph Total harmonic distortion (THD) characteristic (Standard sample used.)

. Application circuit applied.

. LPF: 9th filter applied.