6251-459-2PD

# **Contents**

| Page | Section  | Title                                                           |

|------|----------|-----------------------------------------------------------------|

| 4    | 1.       | Introduction                                                    |

| 4    | 1.1.     | Features                                                        |

| 5    | 1.2.     | Application Overview                                            |

| 5    | 1.2.1.   | Multimedia Mode                                                 |

| 5    | 1.2.2.   | Broadcast Mode                                                  |

| 6    | 2.       | Functional Description of the MAS 3507D                         |

| 6    | 2.1.     | DSP Core                                                        |

| 6    | 2.2.     | Firmware (Internal Program ROM)                                 |

| 7    | 2.3.     | Program Download Feature                                        |

| 7    | 2.4.     | Baseband Processing                                             |

| 7    | 2.4.1.   | Volume Control / Channel Mixer                                  |

| 7    | 2.4.2.   | Mute / Bypass Tone Control                                      |

| 7    | 2.4.3.   | Bass / Treble Control                                           |

| 8    | 2.5.     | Clock Management                                                |

| 8    | 2.6.     | Power Supply Concept                                            |

| 8    | 2.6.1.   | Voltage Monitor                                                 |

| 9    | 2.6.2.   | DC/DC Converter                                                 |

| 9    | 2.6.3.   | Stand-by Functions                                              |

| 9    | 2.6.4.   | Start-up Sequence                                               |

| 10   | 2.7.     | Interfaces                                                      |

| 10   | 2.7.1.   | MPEG Bit Stream Interface                                       |

| 10   | 2.7.2.   | Audio Output Interface                                          |

| 10   | 2.7.2.1. | Mode 1:16 Bits/Sample (I <sup>2</sup> S Compatible Data Format) |

| 10   | 2.7.2.2. | Mode 2:32 Bit/Sample (Inverted SOI)                             |

| 11   | 2.7.2.3. | Other Output Modes                                              |

| 11   | 2.7.3.   | Start-up Configuration                                          |

| 11   | 2.7.4.   | Parallel Input Output Interface (PIO)                           |

| 40   | •        |                                                                 |

| 13   | 3.       | Control Interfaces                                              |

| 13   | 3.1.     | I <sup>2</sup> C Bus Interface                                  |

| 13   | 3.1.1.   | General                                                         |

| 13   | 3.1.2.   | Subaddresses                                                    |

| 14   | 3.1.3.   | I <sup>2</sup> C Registers                                      |

| 14   | 3.1.3.1. | I <sup>2</sup> C Control Register                               |

| 14   | 3.1.3.2. | I <sup>2</sup> C Data Register                                  |

| 14   | 3.2.     | Command Structure                                               |

| 14   | 3.2.1.   | The Internal Fixed Point Number Format                          |

| 14   | 3.2.2.   | Conventions for the Command Description                         |

| 15   | 3.3.     | Detailed MAS 3507D Command Syntax                               |

| 15   | 3.3.1.   | Run                                                             |

| 15   | 3.3.2.   | Read Control Interface Data                                     |

| 16   | 3.3.3.   | Write Register                                                  |

| 16   | 3.3.4.   | Write D0 Memory                                                 |

| 16   | 3.3.5.   | Write D1 Memory                                                 |

| 16   | 3.3.6.   | Read Register                                                   |

| 17   | 3.3.7.   | Read D0 Memory                                                  |

| 17   | 3.3.8.   | Read D1 Memory                                                  |

# Contents, continued

| ,    |          |                                             |

|------|----------|---------------------------------------------|

| Page | Section  | Title                                       |

| 17   | 3.3.9.   | Default Read                                |

| 18   | 3.4.     | Register Table                              |

| 18   | 3.4.1.   | DC/DC Converter                             |

| 20   | 3.4.2.   | Muting / Bypass Tone Control                |

| 20   | 3.4.3.   | Bass and Treble Control                     |

| 22   | 3.5.     | Memory Area                                 |

| 22   | 3.5.1.   | Status Memory                               |

| 22   | 3.5.1.1. | MPEG Frame Counter                          |

| 22   | 3.5.1.2. | MPEG Status 1                               |

| 23   | 3.5.1.3. | MPEG Status 2                               |

| 25   | 3.5.1.4. | CRC Error Counter                           |

| 25   | 3.5.1.5. | Number Of Ancillary Bits                    |

| 25   | 3.5.1.6. | Ancillary Data                              |

| 26   | 3.5.2.   | Configuration Memory                        |

| 27   | 3.5.2.1. | PLL Offset for 44/48 kHz Sampling Frequency |

| 28   | 3.5.2.2. | Output Configuration                        |

| 29   | 3.5.3.   | Baseband Volume Matrix                      |

| 31   | 4.       | Specifications                              |

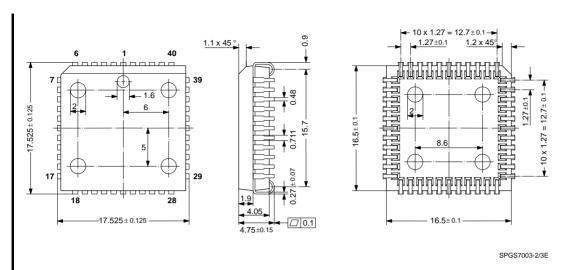

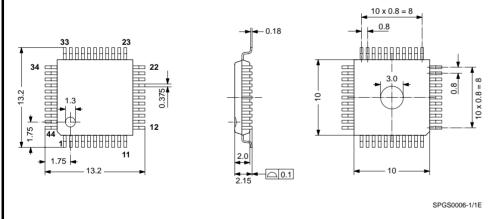

| 31   | 4.1.     | Outline Dimensions                          |

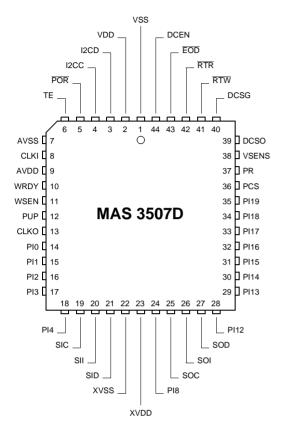

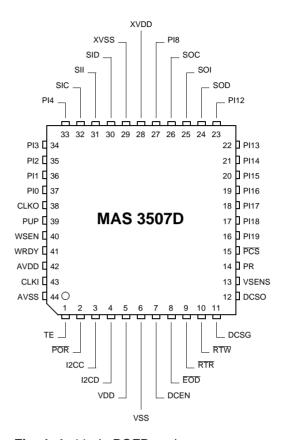

| 32   | 4.2.     | Pin Connections and Short Descriptions      |

| 34   | 4.3.     | Pin Descriptions                            |

| 34   | 4.3.1.   | Power Supply Pins                           |

| 34   | 4.3.2.   | DC/DC Converter Pins                        |

| 34   | 4.3.3.   | Control Lines                               |

| 34   | 4.3.4.   | Parallel Interface Lines                    |

| 34   | 4.3.4.1. | PIO Handshake Lines                         |

| 34   | 4.3.4.2. | PIO Data Lines                              |

| 35   | 4.3.5.   | Voltage Supervision And Other Functions     |

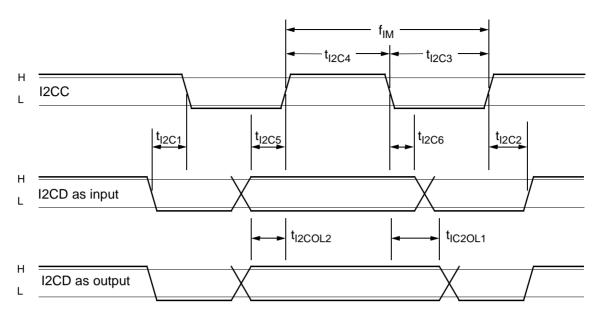

| 35   | 4.3.6.   | Serial Input Interface                      |

| 35   | 4.3.7.   | Serial Output Interface                     |

| 35   | 4.3.8.   | Miscellaneous                               |

| 36   | 4.4.     | Pin Configurations                          |

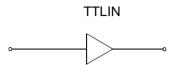

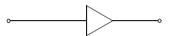

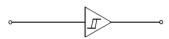

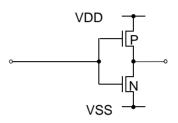

| 37   | 4.5.     | Internal Pin Circuits                       |

| 38   | 4.6.     | Electrical Characteristics                  |

| 38   | 4.6.1.   | Absolute Maximum Ratings                    |

| 38   | 4.6.2.   | Recommended Operating Conditions            |

| 39   | 4.6.3.   | Characteristics                             |

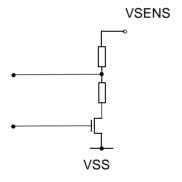

| 40   | 4.6.3.1. | I <sup>2</sup> C Characteristics            |

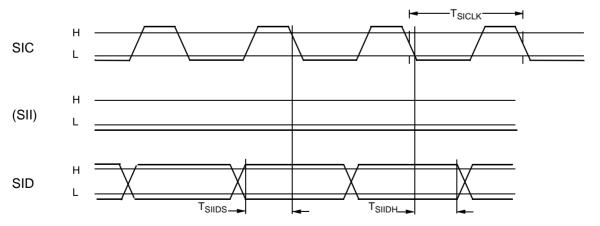

| 41   | 4.6.3.2. | I <sup>2</sup> S Bus Characteristics – SDI  |

| 42   | 4.6.3.3. | I <sup>2</sup> S Characteristics – SDO      |

| 42   | 4.6.4.   | Firmware Characteristics                    |

| 43   | 4.6.4.1. | Timing Parameters of the Demand Mode        |

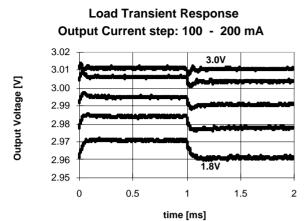

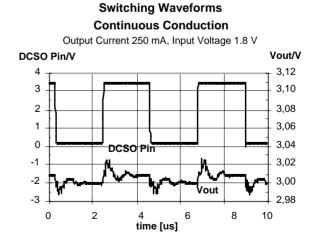

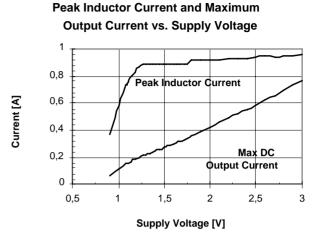

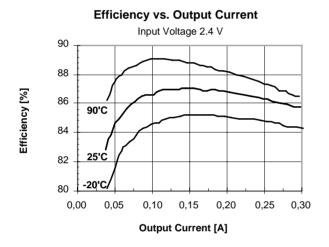

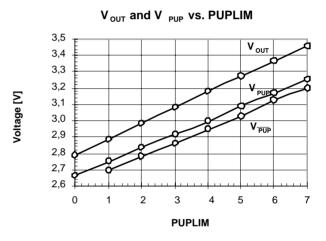

| 44   | 4.6.5.   | DC/DC Converter Characteristics             |

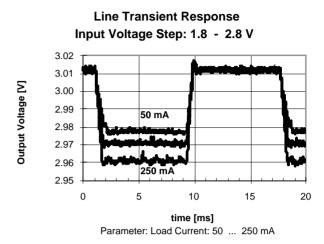

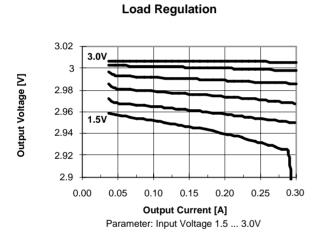

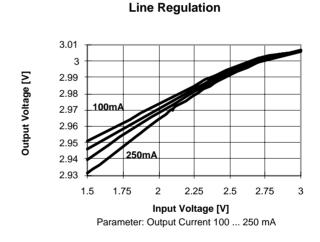

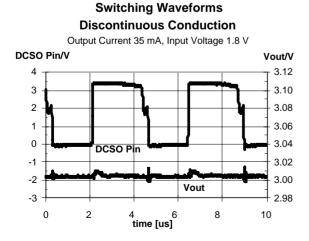

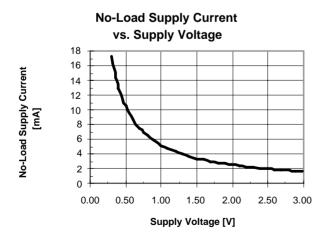

| 46   | 4.6.6.   | Typical Performance Characteristics         |

| 48   | 5.       | Data Sheet History                          |

#### MPEG 1/2 Layer 2/3 Audio Decoder

Release Note: Revision bars indicate significant changes to the previous edition.

#### 1. Introduction

The MAS 3507D is a single-chip MPEG layer 2/3 audio decoder for use in audio broadcast or memory-based playback applications. Due to embedded memories, the embedded DC/DC up-converter, and the very low power consumption, the MAS 3507D is ideally suited for portable electronics.

In MPEG 1 (ISO 11172-3), three hierarchical layers of compression have been standardized. The most sophisticated and complex, layer 3, allows compression rates of approximately 12:1 for mono and stereo signals while still maintaining CD audio quality. Layer 2 (widely used in DVB, ADR, and DAB) achieves a compression of 8:1 providing CD quality.

In order to achieve better audio quality at low bit rates (<64 kbit/s per audio channel), three additional samfrequencies provided by are MPEG 2 (ISO 13818-3). The MAS 3507D decodes both layer 2 and layer 3 bit streams as defined in MPEG 1 and 2. The multichannel/multilingual capabilities defined by MPEG 2 are not supported by the MAS 3507D. An extension to the MPEG 2 layer 3 standard developed by FhG Erlangen, Germany sometimes referenced as MPEG 2.5, for extremely low bit rates at sampling frequencies of 12, 11.025, or 8 kHz is also supported by the MAS 3507D.

## 1.1. Features

- Single-chip MPEG 1/2 layer 2 and 3 decoder

- ISO compliance tests passed

- Extension to MPEG 2 / layer 3 for low bit rates (MPEG 2.5)

- Bit streams with adaptive bit rates (bit-rate switching) are supported.

- Serial asynchronous MPEG bit stream input

- Broadcast and multimedia operation mode

- Automatic locking to given data rate in broadcast mode

- Data request triggered by 'demand signal' in multimedia mode

- Output audio data delivered via an I<sup>2</sup>S bus (in various formats)

- Digital volume / stereo channel mixer / Bass / Treble

- Output sampling clocks are generated and controlled internally.

- Ancillary data provided via I<sup>2</sup>C interface

- Status information accessible via PIO pins or I<sup>2</sup>C

- "CRC Error" and "MPEG Frame Synchronization" Indicators

- Power management for reduced power consumption at lower sampling frequencies

- Low power dissipation (53 mW @  $f_s \le 12$  kHz, 90 mW @  $f_s \le 24$  kHz, 165 mW @  $f_s > 24$  kHz @ 3 V)

- Supply voltage range: 1.6 V to 3.6 V due to built-in DC/DC converter (2-cell battery operation)

- Adjustable power supply supervision

- Power-off function

- Data processing by a high-performance RISC DSP core (MASC)

- Additional functionality achievable via download software (CELP voice Decoder, ADPCM encoder / decoder)

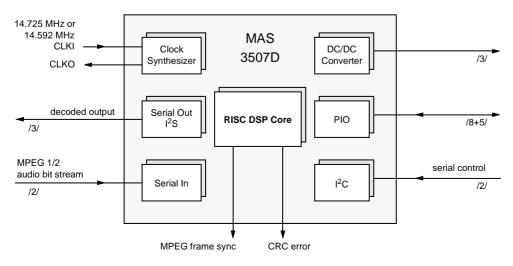

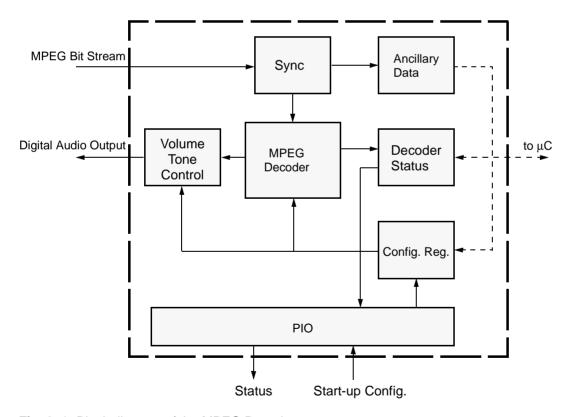

Fig. 1-1: MAS 3507D block diagram

#### 1.2. Application Overview

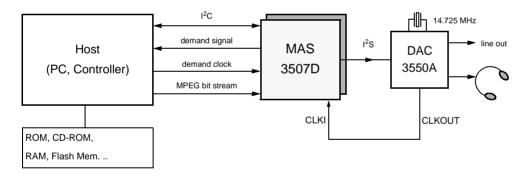

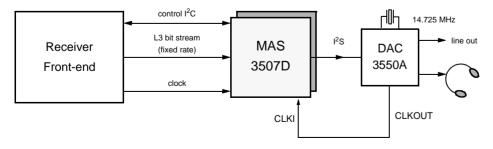

The MAS 3507D can be applied in two major environments: in multimedia mode or in broadcast mode. For both modes, the DAC 3550A fits perfectly to the requirements of the MAS 3507D. It is a high-quality multi sample rate DAC (8 kHz ... 50 kHz) with internal crystal oscillator and integrated stereo headphone amplifier.

#### 1.2.1. Multimedia Mode

In a memory-based multimedia environment, the easiest way to incorporate a MAS 3507D decoder is to use its data-demand pin. This pin can be used directly to request input bit stream data from the host or memory system.

While the demand pin is active, the data stream shall be transmitted to the MAS 3507D. The bit stream clock should be higher than the actual data rate of the MPEG bit stream (1 MHz bit stream clock works with all MPEG bit rates). The demand signal will be active until the input buffer of the MAS 3507D is filled.

A delayed response of the host to the demand signal (by several milliseconds) or an interrupted response of the host will be tolerated by the MAS 3507D as long as the input buffer does not run empty. A PC might use its DMA capabilities to transfer the data in the background to the MAS 3507D without interfering with its foreground processes.

The source of the bit stream may be a memory (e.g. ROM, Flash) or PC peripherals, such as CD-ROM drive, an ISDN card, a hard disk or a floppy disk drive.

#### 1.2.2. Broadcast Mode

In environments where the bit stream is delivered from an independent transmitter to one or more receivers, the MAS 3507D cannot act as master for the bit stream clock. In this mode, it synchronizes itself to the incoming bit stream data rate by a digital PLL and generates a synchronized digital audio sample clock for the required output sample rates.

Fig. 1–2: Block diagram of a MAS 3507D, decoding a stored bit stream in multimedia mode

Fig. 1–3: Block diagram of a MAS 3507D in a broadcast environment

### 2. Functional Description of the MAS 3507D

#### 2.1. DSP Core

The hardware of the MAS 3507D consists of a high performance RISC Digital Signal Processor (DSP) and appropriate interfaces (see Fig. 2–1). The internal processor works with a memory word length of 20 bits and an extended range of 32 bits in its accumulators. The instruction set of the DSP is highly optimized for audio data compression and decompression. Thus, only very small areas of internal RAM and ROM are required. All data input and output actions are based on a 'non cycle stealing' background DMA that does not cause any computational overhead.

# 2.2. Firmware (Internal Program ROM)

A valid MPEG 1/2/2.5 layer 2/3 data signal is taken as input. The signal lines are a clock line SIC and the data line SID. The MPEG decoder performs the audio decoding. The steps for decoding are

- synchronization,

- side information extraction,

- Huffman decoding,

- ancillary data extraction, and

- volume and tone control.

For the supported bit rates and sample rates, see Table 3–11 on page 24. Frame Synchronization and CRC-error signals are provided at the output pins of the MAS 3507D.

Fig. 2-1: Block diagram of the MPEG Decoder

#### 2.3. Program Download Feature

This is an additional feature that is not required for the MPEG decoding function.

The overall function of the MAS 3507D can be altered by downloading up to 1 kWord program code into the internal RAM and executing this code instead of the ROM code. During this time, MPEG decoding is not possible.

The code must be downloaded by the 'write to memory' command (see Section 3.3.) into an area of RAM that is switchable from data memory to program memory. A 'run' command (see Section 3.3.1.) starts the operation.

INTERMETALL provides modules for voice-decoding using the CELP algorithm (performing good speech quality at very low bit rates) and for encoding and decoding audio data with ADPCM.

Otherwise, the customer can write its own modules (knowledge in DSP programming is necessary).

Detailed information about downloading is provided in combination with the MAS 3507D software development package from INTERMETALL.

For commercial issues and detailed information please contact our sales department.

#### 2.4. Baseband Processing

#### 2.4.1. Volume Control / Channel Mixer

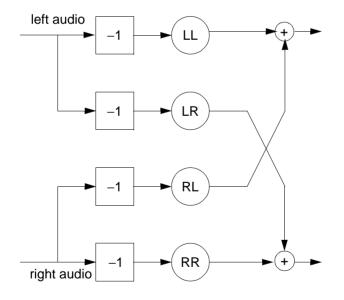

A digital volume control matrix is applied to the digital stereo audio data. This performs additional balance control and a simple kind of stereo basewidth enhancement. The 4 factors LL, LR, RL, and RR are adjustable via the controller with 20-bit resolution. See Fig. 3–2 and Section 3.5.3. for details.

### 2.4.2. Mute / Bypass Tone Control

A special bit enables a fast and simple mute functionality without changing the current volume setting. Another bit allows to bypass the complete bass / treble / volume control. See for details Section 3.4.2..

#### 2.4.3. Bass / Treble Control

Tone control is implemented in the MAS 3507D. It allows the control of bass and treble in a range up to ±15 dB, as Table 3–8 shows. To prevent overflow or clipping effects, the prescaler is built-in. The prescaler decreases the overall gain of the tone filter, so the full range up to +15 dB is usable without clipping.

Due to the different frequency ranges in MPEG 1, MPEG 2, or MPEG 2.5, the bass cutoff frequencies differ

**Table 2–1:** Settings for the digital volume matrix

| Cutoff  | Bass   | Treble |  |  |  |

|---------|--------|--------|--|--|--|

| MPEG1   | 100 Hz | 10 kHz |  |  |  |

| MPEG2   | 200 Hz | 10 kHz |  |  |  |

| MPEG2.5 | 400 Hz | 10 kHz |  |  |  |

For details see Section 3.4.3..

#### 2.5. Clock Management

The MAS 3507D is driven by a single clock at a frequency of 14.592 MHz or, alternatively, 14.725 MHz. It is possible to drive the MAS 3507D with other reference clocks (see Section 3.5.2.1. on page 27).

The *CLKI* signal acts as a reference for the embedded clock synthesizer that generates the internal system clock. Based on the reference input clock *CLKI*, a synchronized output clock *CLKO* that depends on the audio sample frequency of the decompressed bit stream is generated and provided as 'master clock' to external D/A converters. Some DACs need master clocks that have a fixed relation to the sampling frequencies. A scaler can be switched on during start-up, optionally, by activating the *PI8* pin. Then, the clock-out will automatically be divided by 1, 2, or 4 as defined in Table 2–2.

Table 2-2: CLKO Frequencies

| f <sub>s</sub> /kHz | CLKO/MHz<br>scaler on | CLKO/MHz<br>scaler off |

|---------------------|-----------------------|------------------------|

| 48, 32              | 24.576                | 24.576                 |

| 44.1                | 22.5792               | 22.5792                |

| 24, 16              | 12.288                | 24.576                 |

| 22.05               | 11.2896               | 22.5792                |

| 12, 8               | 6.144                 | 24.576                 |

| 11.025              | 5.6448                | 22.5792                |

#### 2.6. Power Supply Concept

The MAS 3507D offers an embedded controlled DC/DC converter for battery based power supply concepts. It works as an up-converter.

## 2.6.1. Voltage Monitor

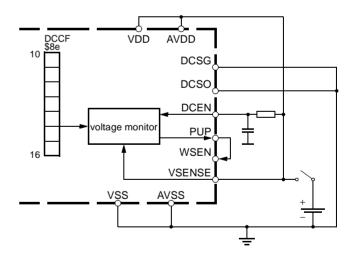

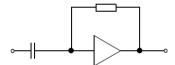

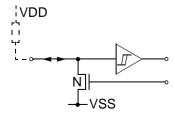

A voltage monitor compares the input voltage at the *VSENS* pin with an internal reference value that is adjustable via I<sup>2</sup>C bus. The *PUP* output pin becomes inactive when the voltage at the *VSENS* pin drops below the reference voltage. The voltage monitor function can be activated independently of the DC/DC converter operation (see Fig. 2–2 for application circuit without DC/DC converter functionality).

The *PUP* signal can be read out by the system controller. The controller again may be connected with the corresponding input line *WSEN* of the MAS 3507D to activate MPEG decoding. It is important that the *WSEN* must not be activated before the *PUP* is generated. In applications without controller, it is recommended to connect *PUP* with *WSEN*. The PUP signal thresholds are listed in Table 3–7.

Note: Be careful in case of direct connection of *PUP* and *WSEN*. Do not set the PUP voltage to high, otherwise *PUP* and *WSEN* goes down and it is not possible to set the old PUP level by I<sup>2</sup>C command.

**Fig. 2–2:** Voltage monitor connections, DC/DC converter not used

#### 2.6.2. DC/DC Converter

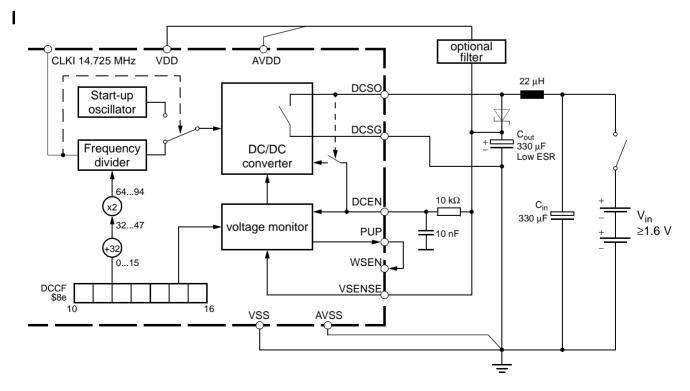

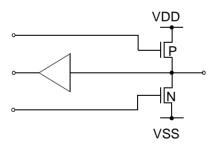

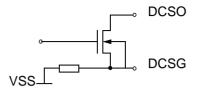

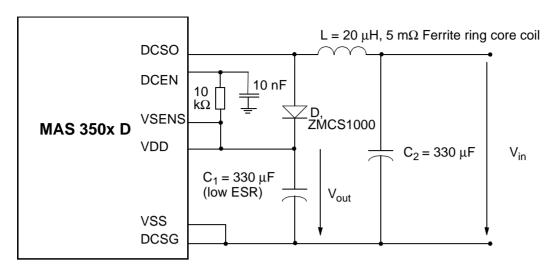

The DC/DC converter of the MAS 3507D is used to generate a fixed power supply voltage even if the chip set is powered by battery cells in portable applications. The DC/DC converter is designed for the application of 2 batteries or NiCd cells as shown in Fig. 2–3 which shows the standard application circuit. The DC/DC converter is switched on by activating the *DCEN* pin. Its output power is sufficient for other ICs as well.

Note: Connecting *DCEN* directly to VDD leads to unexpected states.

The *PUP* signal can be read out by the system controller. The controller again may be connected with the corresponding input line *WSEN* of the MAS 3507D to activate MPEG decoding. It is important that the *WSEN* signal must not be activated before the *PUP* signal is high. In applications without controller it is recommended to connect *PUP* with *WSEN*. The *PUP* signal thresholds are listed in Table 3–7.

**Note:** Be careful in case of direct connection of *PUP* and *WSEN*. Do not set the *PUP* voltage to high, otherwise *PUP* and *WSEN* goes down and it is not possible to set the old *PUP* level by I<sup>2</sup>C command.

A  $22\,\mu H$  inductor is required for the application. The important specification item is the inductor saturation current rating, which should be greater than 2.5 times the DC load current. The DC resistance of the inductor

is important for efficiency. The primary criterion for selecting the output filter capacitor is low equivalent series resistance (ESR), as the product of the inductor current variation and the ESR determines the high-frequency amplitude seen on the output voltage. The Schottky diode should have a low voltage drop  $\rm U_D$  for a high overall efficiency of the DC/DC converter. The current rating of the diode should also be greater than 2.5 times the DC output current. The  $\it VSENS$  pin is always connected to the output voltage at low ESR capacitance.

# 2.6.3. Stand-by Functions

Both the digital part of the MAS 3507D and the DC/DC converter have their own power-up pins (*WSEN*, *DCEN*). Thus, the DC/DC converter can remain active to supply other parts of the application even if the audio decoding part of the MAS 3507D is not being used. The *WSEN* power-up pin of the digital part may be handled by the controller.

Please pay attention to the fact, that I<sup>2</sup>C protocol is working only if the processor and its interfaces works (*DCEN*=1 & *WSEN*=1)

#### 2.6.4. Start-up Sequence

The DC/DC converter is switched on by activating the *DCEN* pin. After *PUP* and *WRDY* are high set *WSEN*.

Fig. 2-3: DC/DC converter connections

#### 2.7. Interfaces

The MAS 3507D uses an I<sup>2</sup>C control interface, a serial input interface for MPEG bit stream, and a digital audio output interface for the decoded audio data (I<sup>2</sup>S or similar). Additionally, a parallel I/O interface (PIO) may be used for monitoring and mode selection tasks. The PIO lines are defined by the internal firmware.

#### 2.7.1. MPEG Bit Stream Interface

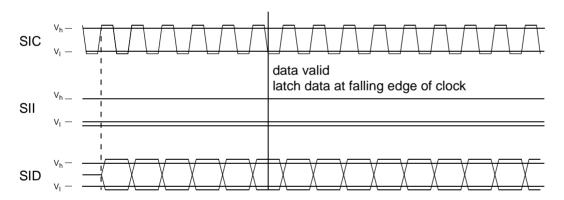

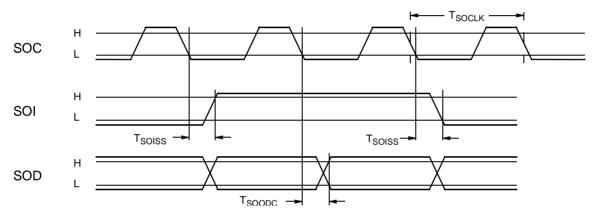

The MPEG bit stream input interface consists of the three pins: *SIC*, *SII*, and *SID*. For MPEG decoding operation, the SII pin must always be connected to VSS. The MPEG input signal format is shown in Fig. 2–4. The data values are latched with the falling edge of the *SIC* signal.

The MPEG bit stream generated by an encoder is unformatted. It will be formatted (e.g. 8 bit or 16 bit) by storing at a media (PC, EEPROM). The serial data required from the MPEG bit stream interface must be in the same bit order as produced by the encoder.

#### 2.7.2. Audio Output Interface

The audio output interface of the MAS 3507D is a standard I<sup>2</sup>S interface. It is possible to choose between two standard interfaces (16 bit with delay or 32 bit with inverted *SOI*) via start-up configuration. These setup modes meet the performance of the most common DACs. It is also possible to select other interface modes via I<sup>2</sup>C commands (see Section 2.7.2.3.).

# 2.7.2.1. Mode 1:16 Bits/Sample (I<sup>2</sup>S Compatible Data Format)

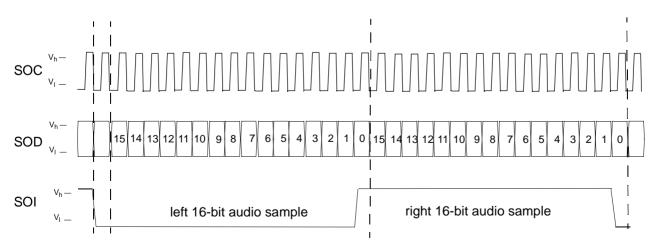

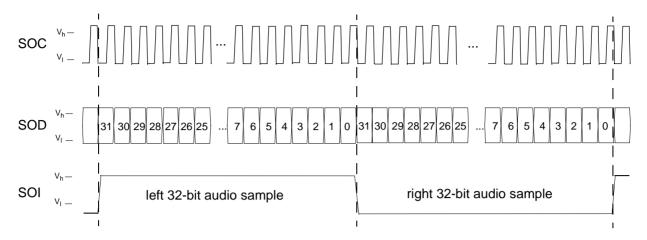

A schematic timing diagram of the SDO interface in 16 bit/sample mode is shown in Fig. 2–5.

#### 2.7.2.2. Mode 2:32 Bit/Sample (Inverted SOI)

If the serial output generates 32 bits per audio sample, only the first 20 bits will carry valid audio data. The 12 trailing bits are set to zero by default (see Fig. 2–6).

Fig. 2-4: Schematic timing of the SDI (MPEG) input

Fig. 2-5: Schematic timing of the SDO interface in 16 bit/sample mode

Fig. 2-6: Schematic timing of the SDO interface in 32 bit/sample mode

### 2.7.2.3. Other Output Modes

The interface is also configurable by software to work in different modes. It is possible to choose:

- 16 or 32 bit/sample modes,

- inverted or not inverted word strobe (SOI).

- no delay or delay of data related to word strobe.

For further details see Section 3.5.2.2.

#### 2.7.3. Start-up Configuration

Basic operation of the MAS 3507D is possible without controller interaction. Configuration and the most important status information are available by the PIO interface. The start-up configuration is selected according to the levels of several PIO pins. The levels should be set via high impedance resistors (for example 10  $k\Omega$ ) to VSS or VDD and will be copied into the StartupConfig register directly after power up / reset. After start-up, the PIO will be reconfigured as output.

To enable greater flexibility, it is possible to configure the MAS 3507D without using the PIO pins or to reconfigure the IC after start-up. The procedure for this is to send two I<sup>2</sup>C commands to the MAS 3507D:

- Writing the StartupConfig register (see Section 3.4. on page 18)

- Execute a 'run \$0fcd' command (see Section 3.3.1.).

The configuration will be active up to a reset. Then, the new configuration will be loaded again via PIO.

### 2.7.4. Parallel Input Output Interface (PIO)

The parallel interface of the MAS 3507D consists of the lines *PIO...PI4*, *PI8*, *PI12...PI19*, and several control lines. During start-up, the PIO will read the start-up configuration. This is to define the environment for the MAS 3507D. The following pins must be connected via resistors to *VSS* or *VDD*:

**Table 2–3:** Start-up configuration<sup>1)</sup>

| PIO<br>Pin | "0"                                                                 | "1"                                       |

|------------|---------------------------------------------------------------------|-------------------------------------------|

| PI8        | divide CLKO by 1,<br>2, or 4 (according<br>to MPEG 1, 2, or<br>2.5) | CLKO fixed at<br>24.576 or 22.5792<br>MHz |

| PI4        | 14.725 MHz input clock                                              | 14.592 MHz input<br>clock                 |

| PI3        | Enable layer 3                                                      | Disable layer 3                           |

| PI2        | Enable layer 2                                                      | Disable layer 2                           |

| PI1        | SDO output: 32 bit                                                  | SDO output: 16 bit                        |

| PI0        | input: Multimedia<br>mode (PLL off)                                 | input: Broadcast<br>mode (PLL on)         |

<sup>1)</sup> Start-up setting can be overruled by I2C commands after reset.

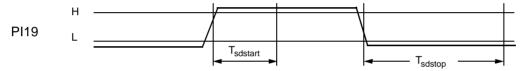

After having read the start-up configuration, the PIO will be switched to ' $\mu$ P-mode'. In  $\mu$ P-mode, the additional PIO control lines (PR,  $\overline{PCS}$ ) are evaluated. The MPEG decoder firmware expects PR = '1' and the  $\overline{PCS}$  = '0'. Then, all PIO interface lines are configured as output and display some status information of the MPEG decoder. The PIO lines can be read by an external controller or directly used by dedicated hardware blocks (e.g. for sample rate indication or display units). The internal MPEG decoder firmware attaches specific functions to the following pins:

Table 2-4: PIO output signals during MPEG decoding

| PIO<br>Pin | Name                     | Comment                                                       |

|------------|--------------------------|---------------------------------------------------------------|

| PI19       | Demand PIN               |                                                               |

|            | %0<br>%1                 | no input data exp.<br>input data request                      |

| PI18,      | MPEG INDEX               |                                                               |

| PI17       | %00<br>%01<br>%10<br>%11 | MPEG 2.5<br>reserved<br>MPEG 2<br>MPEG 1                      |

| PI13,      | MPEG Layer ID            |                                                               |

| PI12       | %00<br>%01<br>%10<br>%11 | reserved<br>Layer 3<br>Layer 2<br>Layer 1 <sup>1)</sup>       |

| PI8        | MPEG CRC-ERROR           |                                                               |

|            | %0<br>%1                 | no error<br>CRC-error,<br>MPEG decoding<br>not successful     |

| PI4        | MPEG-FRAME-<br>SYNC      | see following text                                            |

| PI3,       | Sampling frequency       | in kHz <sup>2)</sup>                                          |

| PI2        | %00<br>%01<br>%10<br>%11 | 44.1 / 22.1 / 11.0<br>48 / 24 / 12<br>32 / 16 / 8<br>reserved |

| PI1,       | Deemphasis               |                                                               |

| PI0        | %00<br>%01<br>%10<br>%11 | none<br>50/15 μs<br>reserved<br>CCITT J.17                    |

<sup>1)</sup>Layer 1 bit streams will not be decoded

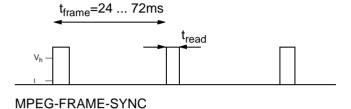

The MPEG-FRAME-SYNC signal is set to '1' after the internal decoding for the MPEG header has been finished for one frame. The rising edge of this signal could be used as an interrupt input for the controller that triggers the read out of the control information and ancillary data. As soon as the MAS 3507D has recognized the corresponding read command ('read control interface data' (see Section 3.3.2. on page 15), the MPEG-FRAME-SYNC is reset. This behavior reduces the possibility of missing the MPEG-FRAME-SYNC active state.

Fig. 2-7: Schematic timing of MPEG-FRAME-Sync

The time  $t_{\text{read}}$  depends on the response time of the controller. This time must not exceed 1/2 of the MPEG-frame length  $t_{\text{frame}}$ . The MPEG frame lengths are given in Table 2–5.

Table 2-5: Frame length in MPEG layer 2 / 3

| f <sub>s</sub> in<br>kHz | Frame Length<br>Layer 2 | Frame Length<br>Layer 3 |

|--------------------------|-------------------------|-------------------------|

| 48                       | 24 ms                   | 24 ms                   |

| 44.1                     | 26.12 ms                | 26.12 ms                |

| 32                       | 36 ms                   | 36 ms                   |

| 24                       | 48 ms                   | 24 ms                   |

| 22.05                    | 52.24 ms                | 26.12 ms                |

| 16                       | 72 ms                   | 32 ms                   |

| 12                       | not available           | 48 ms                   |

| 11.025                   | not available           | 52.24 ms                |

| 8                        | not available           | 72 ms                   |

<sup>&</sup>lt;sup>2)</sup>Sampling frequency also defined by MPEG index (see Table 3–11 for additional information)

#### 3. Control Interfaces

#### 3.1. I<sup>2</sup>C Bus Interface

#### **3.1.1. General**

Communication between the MAS 3507D and the external controller is done via  $I^2C$  bus. An  $I^2C$  slave interface with a minimum transfer data word length of 16 bits is provided. The interface uses one level of subaddresses. The device addresses are shown in Table 3–1.  $I^2C$  clock synchronization is used to slow down the interface if required.

Table 3-1: I<sup>2</sup>C device address

| A7 | A6 | A5 A4 |   | А3 | A2 | A1 | W/R |

|----|----|-------|---|----|----|----|-----|

| 0  | 0  | 1     | 1 | 1  | 0  | 1  | 0/1 |

The I<sup>2</sup>C data and control registers of the MAS 3507D have 16-bit data size. They are accessed by reading/ writing two 8-bit data words.

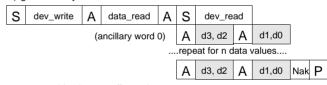

Fig. 3–1 shows I<sup>2</sup>C bus protocols for read and write operations of the interface; the read operation requires an extra start condition and repetition of the chip address with read command set.

Please pay attention to the fact that I<sup>2</sup>C protocol works only if the processor is working (DCEN=1 & WSEN=1)

#### 3.1.2. Subaddresses

The  $I^2C$  control interface of the MAS 3507D is designed as a slave interface. A system controller may send configuration commands or read status information via the  $I^2C$  interface. The  $I^2C$  interface has 3 subaddresses allocated.

Table 3-2: Subaddresses

| Sub-<br>addresses | Comment                                         |

|-------------------|-------------------------------------------------|

| \$68 /write       | controller writes to MAS 3507D data register    |

| \$69 /read        | controller reads from MAS 3507D data register   |

| \$6A/ write       | controller writes to MAS 3507D control register |

The address (\$6a) is used for basic control, i.e. reset and task select. The other addresses are used for data transfer from/to the MAS 3507D.

Example: I<sup>2</sup>C write access

| S  | dev_write (\$3A) | Ack                   | data_write (\$68) | Ack | Ack high byte data Ack |              | lov | v byte data | Ac          | k P  |     |   |

|----|------------------|-----------------------|-------------------|-----|------------------------|--------------|-----|-------------|-------------|------|-----|---|

|    | Examp            | ole: I <sup>2</sup> C | C read access     |     |                        |              |     |             |             |      |     |   |

| S  | dev_write (\$3A) | Ack                   | data_read (\$69)  | Ack | S                      | dev_read (\$ | 3b) | Ack         | high byte o | data | Ack |   |

|    |                  |                       | •                 | •   | •                      | •            |     |             | low byte d  | ata  | Nak | Р |

| SI | DA               |                       | 1                 | _   |                        | г — ¬        |     | W           | = 0         |      |     |   |

Fig. 3–1: I<sup>2</sup>C bus protocol for the MAS 3507D

# 3.1.3. I<sup>2</sup>C Registers

# 3.1.3.1. I<sup>2</sup>C Control Register

The I<sup>2</sup>C control register is a write-only register and its main purpose is the software reset of the MAS 3507D.

**Table 3–3:** Control register bit assignment<sup>1)</sup>

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| x  | х  | х  | х  | х  | х  | х  | R  | 0  | 0  | 0  | 0  | Т3 | T2 | T1 | T0 |

<sup>1)</sup> x = don't care, R = reset, T3...T0 = task selection

The software reset is done by writing a 16-bit word to the MAS 3507D with 'bit 8' set. The 4 least significant bits are reserved for task selection. The task selection is only useful in combination with download software. In standard MPEG decoding, these bits must always be set to '0'.

# 3.1.3.2. I<sup>2</sup>C Data Register

The I<sup>2</sup>C data register is readable (subaddress data\_read), writable (subaddress data\_write), and has a length of 16 bits. The data transfer is done with the most significant bit (m) first.

Table 3-4: Data register bit assignment

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| m  |    |    |    |    |    |    |    |    |    |    |    |    |    |    | _  |

#### 3.2. Command Structure

The I<sup>2</sup>C control of the MAS 3507D is done completely via the I<sup>2</sup>C data register by using a special command syntax. The commands are executed by the MAS 3507D during its normal operation without any loss or interruption of the incoming data or outgoing audio data stream. These I<sup>2</sup>C commands allow the controller to access internal states, RAM contents, internal hardware control registers, and even a download of an alternative software module. The command structure allows sophisticated control of the MAS 3507D. The registers of the MAS 3507D are either general purpose, e.g. for program flow control, or specialized registers that directly affect hardware blocks. The unrestricted access to these registers allows the system controller to overrule the firmware configuration of the serial interfaces or the default input line selection.

The control interface is also used for low bit rate data transmission, e.g. MPEG-embedded ancillary data

transmission. The data information is performed by sending a 'read memory' command to the MAS 3507D and by reading the memory block that temporarily contains the required information. The synchronization between the controller and the MAS 3507D is done via a MPEG-FRAME-SYNC signal or by monitoring the MPEGFrameCount register (at the cost of a higher work load for the controller).

The MAS 3507D firmware scans the I<sup>2</sup>C interface periodically and checks for pending or new commands. However, due to some time critical firmware parts, a certain latency time for the response has to be expected. The theoretical worst case response time does not exceed 4 ms. However, the typical response time is less than 0.5 ms. Table 3–5 shows the basic controller commands that are available by the MAS 3507D

#### 3.2.1. The Internal Fixed Point Number Format

Internal register or memory values can easily be accessed via the I<sup>2</sup>C interface. In this document, two number representations are used: the fixed point notation 'v' and the 2's complement number notation 'r'.

The conversion between the two forms of notation is easily done (see the following equations).

$$r = v*524288.0+0.5$$

;  $(-1.0 \le v < 1.0)$  (EQ 1)

$$v = r/524288.0$$

; (-524288 < r < 524287) (EQ 2)

#### 3.2.2. Conventions for the Command Description

The description of the various controller commands uses the following formalism:

- A data value is split into 4-bit nibbles which are numbered beginning with 0 for the least significant nibble.

- Data values in nibbles are always shown in hexadecimal notation indicated by a preceding \$.

- A hexadecimal 20-bit number d is written, e.g. as d = \$17C63, its five nibbles are d0 = \$3, d1 = \$6, d2 = \$C, d3 = \$7, and d4 = \$1.

- Abbreviations used in the following descriptions:

- a address

- d data value

- n count value

- o offset value

- r register number

- x don't care

- Variables used in the following descriptions:

dev\_write \$3a dev\_read \$3b data\_write \$68 data\_read \$69 control \$6a

Table 3-5: Basic controller commands

| Code       | Command                                          | Comment                                                                                                                 |

|------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| \$0<br>\$1 | run                                              | Start execution of an internal program. (Run 0 means freeze operating system.)                                          |

| \$3        | read Control Informa-<br>tion and Ancillary Data | fast read of a block of information organized in 16-bit words (see Section 3.5.1. on page 22)                           |

| \$9        | write register                                   | An internal register of the MAS 3507D can be written directly to by the controller.                                     |

| \$A<br>\$B | write to memory                                  | A block of the DSP memory can be written to by the controller. This feature may be used to download alternate programs. |

| \$D        | read register                                    | The controller can read an internal register of the MAS 3507D.                                                          |

| \$E<br>\$F | read memory                                      | A block of the DSP memory can be read by the controller.                                                                |

#### 3.3. Detailed MAS 3507D Command Syntax

#### 3.3.1. Run

| S | dev_write | Α   | data_write | Α   | a3,a2 | Α   | a1,a0 | Α   | Р |

|---|-----------|-----|------------|-----|-------|-----|-------|-----|---|

| _ | _         | , . | _          | , . | ,     | , . | ,     | , . |   |

The 'run' command causes the start of a program part at address  $\mathbf{a} = (a3,a2,a1,a0)$ . The nibble a3 is restricted to \$0 or \$1 which also acts as command selector. Run with address  $\mathbf{a} = \$0$  will suspend normal MPEG decoding and only I<sup>2</sup>C commands are evaluated. This freezing will be required if alternative software is downloaded into the internal RAM of the MAS 3507D. Detailed information about downloading is provided in combination with a MAS 3507D software development package or together with MAS 3507D software modules available from INTERMETALL.

If the address \$1400  $\leq$  **a** < \$1800, the MAS 3507D continues execution of the program with the downloaded code. For detailed information, please refer to the MASC software development kit. This is for starting the downloaded program code.

Example 1: '*run*' at address \$fcd (override start-up configuration) has the following I<sup>2</sup>C protocol:

<\$3a><\$68><\$0f><\$cd>

Example 2: 'run' at address \$fcb (activate PLLOffset and OutputConfig after change by write command) has the following I<sup>2</sup>C protocol:

<\$3a><\$68><\$0f><\$cb>

#### 3.3.2. Read Control Interface Data

1) send command

2) get ancillary data values

x2...x0: combined count, offset value d3...d0: 16-bit data values

An internal memory array keeps the status information of the MAS 3507D (see Table 3–9). The 'read control interface data' command can be used for quick access to this memory array. A successive range of memory locations may be read by passing a 6-bit offset value "o" and a 6-bit count value "n" as parameter.

Both values are combined in a 12-bit = 4 nibble field x2, x1, x0. If, for example, 4 words (n=4) starting with one word offset (o=2), i.e. the MPEGStatus2, the CRCErrorCount, and NumberOfAncillaryBits are read from the control memory array, the 3 nibbles x2, x1 and x0 are evaluated as shown in the following table.

|              | 11    | 10        | 9 | 8 | 7 | 6 | 5                  | 4 | 3 | 2 | 1 | 0 |

|--------------|-------|-----------|---|---|---|---|--------------------|---|---|---|---|---|

| 6-bit values | offse | offset: 2 |   |   |   |   | number of words: 3 |   |   |   |   |   |

| bit          | 0     | 0         | 0 | 0 | 1 | 0 | 0                  | 0 | 0 | 0 | 1 | 1 |

| nibble       | 0     |           |   |   | 8 |   |                    |   | 3 |   |   |   |

# The complete I<sup>2</sup>C protocol reads as:

```

<$3a><$68><$30><$83>

<$3a><$69><$3b><receive 3 16-bit data values>

```

The 'read control interface data' command resets the MPEG-FRAME-SYNC at PI4 pin (see Section 2.7.4. on page 11).

### 3.3.3. Write Register

| S | dev_write | Α | data_write | Α | <b>\$9</b> , r1 | Α | r0, d0 | Α |   |

|---|-----------|---|------------|---|-----------------|---|--------|---|---|

|   |           |   |            |   | d4, d3          | Α | d2, d1 | Α | Р |

The controller writes the 20-bit value  $(\mathbf{d} = d4, d3, d2, d1, d0)$  into the MAS 3507D register  $(\mathbf{r} = r1, r0)$ . In contrast to memory cells, registers are always addressed individually, and they may also interact with built-in hardware blocks. A list of useful registers is given in the next section.

Example: Muting can be realized by writing the value 1 into the register with the number \$aa:

<\$3a><\$68><\$9a><\$a1><\$00><\$00>

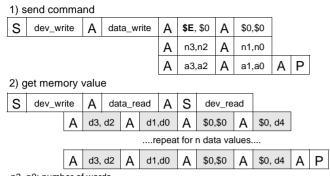

### 3.3.4. Write D0 Memory

| S | dev_write | Α | data_write | Α   | <b>\$A</b> , \$0 | Α    | \$0,\$0 |   |   |

|---|-----------|---|------------|-----|------------------|------|---------|---|---|

|   |           |   |            | Α   | n3,n2            | Α    | n1,n0   |   |   |

|   |           |   |            | Α   | a3,a2            | Α    | a1,a0   |   |   |

|   |           |   |            | Α   | d3,d2            | Α    | d1,d0   |   |   |

|   |           |   |            | Α   | \$0,\$0          | Α    | \$0,d4  |   |   |

|   |           |   | -          | rep | eat for n        | data | values  | • |   |

|   |           |   |            | Α   | d3,d2            | Α    | d1,d0   |   |   |

|   |           |   |            | Α   | \$0,\$0          | Α    | \$0,d4  | Α | Ρ |

n3..n0: number of words

a3..a0: start address in MASD memory

d4..d0: data value

The MAS 3507D has 2 memory areas of 2048 words each called D0 and D1 memory. For both memory areas, read and write commands are provided.

Example: reconfiguration of the output to 16 bit without delay has the following I<sup>2</sup>C protocol:

```

<$3a><$68><$a0><$00> (write D0 memory)

<$00><$01> (1 word to write)

<$03><$2f> (start address)

<$00><$10> (value = $00010)

<$00><$3a><$68><$0f><$cd> (run command)

```

## 3.3.5. Write D1 Memory

| S | dev_write | Α | data_write | Α   | <b>\$B</b> , \$0 | Α    | \$0,\$0 |   |   |

|---|-----------|---|------------|-----|------------------|------|---------|---|---|

|   |           |   |            | Α   | n3,n2            | Α    | n1,n0   |   |   |

|   |           |   |            | Α   | a3,a2            | Α    | a1,a0   |   |   |

|   |           |   |            | Α   | d3,d2            | Α    | d1,d0   |   |   |

|   |           |   |            | Α   | \$0,\$0          | Α    | \$0,d4  |   |   |

|   |           |   | -          | rep | eat for n        | data | values  |   |   |

|   |           |   |            | Α   | d3,d2            | Α    | d1,d0   |   |   |

|   |           |   |            | Α   | \$0,\$0          | Α    | \$0,d4  | Α | I |

n3..n0: number of words to be transmitted a3. a0: start address in MASD memory

d4..d0: data value

For further details, see 'write D0 memory' command.

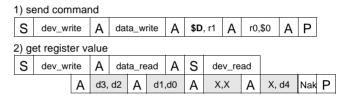

## 3.3.6. Read Register

r1, r0: register **r** d3...d0: data value in **r** X: don't care

The MAS 3507D has an address space of 256 registers. Some of the registers ( $\mathbf{r}=r1,r0$  in the figure above) are direct control inputs for various hardware blocks, others do control the internal program flow. In the next section, those registers that are of any interest with respect to the MPEG decoding are described in detail.

## Example:

Read the content of the PIO data register (\$c8):

<\$3a><\$68><\$dc><\$80>

<\$3a><\$69><\$3b>

now read:

<d3,d2><d1,d0><x,x><x,d4>

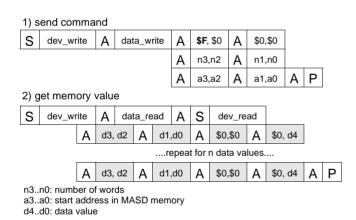

#### 3.3.7. Read D0 Memory

n3..n0: number of words a3..a0: start address in MASD memory

d4..d0: data value

The 'read D0 memory' command is provided to get information from memory cells of the MAS 3507D. It gives the controller access to all memory cells of the internal D0 memory. Direct access to memory cells is an advanced feature of the DSP. It is intended for users of the MASC software development kit.

### 3.3.8. Read D1 Memory

The 'read D1 memory' command is provided to get information from memory cells of the MAS 3507D. It gives the controller access to all memory cells of the internal D1 memory.

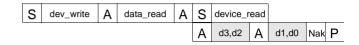

#### 3.3.9. Default Read

The 'default read' command immediately returns the content of the MPEGFrameCount (D0:\$300) of the MAS 3507D in the variable (**d** = d3,d2,d1,d0). The 'default read' command is the fastest way to get information from the MAS 3507D. Executing the 'default read' command in a polling loop can be used to detect the availability of new ancillary data.

# 3.4. Register Table

In Table 3–6, the internal registers that are useful for controlling the MAS 3507D are listed. They are accessible by 'register read/write' I<sup>2</sup>C commands (see Section 3.3. on page 15).

**Important note!** Writing into undocumented registers or read-only registers is always possible, but it is highly recommended not to do so. It may damage the function of the firmware and may even lead to a complete system crash of the decoder operation which can only be restored by a reset.

Table 3-6: Command Register Table

| Address | R/W | Name                          | Comment                                                                                                                                                                                             | Default |

|---------|-----|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| \$8e    | w   | DCCF                          | Set DC/DC converter mode (see Table 3–7 on page 19)                                                                                                                                                 | \$08000 |

| \$aa    | r/w | Mute / Bypass<br>Tone Control | Forces a mute of the digital output bypass Bass / Treble / Volume matrix                                                                                                                            | \$0     |

| \$c8    | r   | PIOData                       | Read back the PIO pin levels. The PI0 pin corresponds to bit 0 in the PIOData register.  This register can be used to detect the actual state of the PIO pins, regardless of the PIO configuration. |         |

| \$e6    | r/w | StartupConfig                 | Shadows the start-up configuration set via PIO pins or I <sup>2</sup> C command (valid are bits 8, 40 as described in Table 2–3.                                                                    |         |

| \$e7    | r/w | KPrescale                     | responsible for prescale of the tone filter (prevent overflows) (see Section 3.4.3. on page 20)                                                                                                     | \$80000 |

| \$6b    | r/w | KBass                         | responsible for increase / decrease of low frequencies (see Section 3.4.3. on page 20)                                                                                                              | \$0     |

| \$6f    | r/w | KTreble                       | responsible for increase / decrease of high frequencies (see Section 3.4.3. on page 20)                                                                                                             | \$0     |

#### 3.4.1. DC/DC Converter

| Address | R/W | Name | Function                 | Default |

|---------|-----|------|--------------------------|---------|

| \$8e    | w   | DCCF | Controls DC/DC operation | \$08000 |

The DCCF Register is controls both the voltage monitor and DC/DC converter. Between output voltage of the DC/DC converter and the voltage monitor threshold an offset exists which is shown in the following table. Please pay attention to the fact, that I<sup>2</sup>C protocol is working only if the processor works (DCEN=1 & WSEN=1). However, the setting for the DCCF register will remain active if the DCEN and WSEN lines are deasserted.

Table 3-7: Bit Assignment of the DCCF register

| Bits | Signal                                                       | Function                                                                                                                                        |                                                                              |

|------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1614 | PUPLIMIT<br>(3 bits)                                         | DC/DC converter output                                                                                                                          | Voltage monitor (PUP signal becomes inactive when output below)              |

|      | 0<br>1<br>2 (reset)<br>3<br>4<br>5<br>6<br>7                 | 2.8 V<br>2.9 V<br>3.0 V<br>3.1 V<br>3.2 V<br>3.3 V<br>3.4 V<br>3.5 V                                                                            | 2.59 V<br>2.69 V<br>2.78 V<br>2.85 V<br>2.95 V<br>3.03 V<br>3.13 V<br>3.20 V |

| 1310 | DCFR (4 bits)  0 (reset) 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | Sets the clock frequency of the 230 kHz 223 kHz 216 kHz 210 kHz 204 kHz 199 kHz 188 kHz 184 kHz 175 kHz 175 kHz 167 kHz 163 kHz 160 kHz 156 kHz | e DC/DC converter to:                                                        |

The DC/DC converter may generate interference noise that could be unacceptable for some applications. Thus the oscillator frequency may be adjusted in 16 steps in order to allow the system controller to select a base frequency that does not interfere with an other application.

The CLKI input provides the base clock  $f_{clki}$  for the frequency divider whose output is made symmetrical with an additional divider by two. The divider quotient is determined by the content of the DCCF register. This register may have values between 0 and 15 generating a DC/DC converter clock frequency  $f_{dc}$  between:

$$f_{dc} = \frac{f_{clki}}{2 \cdot (32 + n)} \bigg|_{n \in \{0, 15\}}$$

(EQ 3)

MICRONAS INTERMETALL

# 3.4.2. Muting / Bypass Tone Control

| Address | R/W | Name                          | Comment                                                                                                    | Default |

|---------|-----|-------------------------------|------------------------------------------------------------------------------------------------------------|---------|

| \$aa    | r/w | Mute / Bypass<br>Tone Control | Forces a mute of the digital output                                                                        | \$0     |

|         |     | 0<br>1<br>2                   | no mute, Tone control active<br>mute output, but continue decoding<br>bypass Bass / Treble / Volume matrix |         |

To enable fast and simple mute functionality, set bit 0 in register \$aa to '1'. Writing a '0' deactivates mute.

It is possible to bypass the complete bass / treble / volume control by setting bit 1 in register \$aa (write a '2'). Resetting bit 1 to '0' enables tone control again.

### 3.4.3. Bass and Treble Control

| Address | R/W | Name      | Comment                                                                                        | Default |

|---------|-----|-----------|------------------------------------------------------------------------------------------------|---------|

| \$e7    | r/w | KPrescale | responsible for prescale of the tone filter (prevent overflows) (see Section 2.4.3. on page 7) | \$80000 |

| \$6b    | r/w | KBass     | responsible for increase / decrease of low frequencies (see Section 2.4.3. on page 7)          | \$0     |

| \$6f    | r/w | KTreble   | responsible for increase / decrease of high frequencies (see Section 2.4.3. on page 7)         | \$0     |

Tone control is implemented in the MAS 3507D. It allows the control of bass and treble in a range up to ±15 dB, as Table 3–8 shows. To prevent overflow or clipping effects, the prescaler is built-in. The prescaler decreases the overall gain of the tone filter, so the full range up to +15 dB is usable without clipping.

To select a special setting, max. 3 coefficients have to be written into registers of the MAS 3507D. This has to be done via the 'write register'  $I^2C$  command (see Section 3.3.3.).

Table 3–8: Tone control registers

| ı | Boost in dB | Bass (Reg. \$6b) | Treble (Reg. \$6f) | Prefactor (Reg \$e7) |

|---|-------------|------------------|--------------------|----------------------|

|   | +15         | \$61800          | \$5f800            | \$e9400              |

|   | +14         | \$5d400          | \$58400            | \$e6800              |

|   | +13         | \$58800          | \$51800            | \$e3400              |

|   | +12         | \$53800          | \$49c00            | \$dfc00              |

|   | +11         | \$4e400          | \$42c00            | \$dc000              |

|   | +10         | \$48800          | \$3c000            | \$d7800              |

|   | +9          | \$42800          | \$35400            | \$d25c0              |

|   | +8          | \$3c000          | \$2ec00            | \$cd000              |

|   | +7          | \$35800          | \$28400            | \$c6c00              |

|   | +6          | \$2e400          | \$22000            | \$bfc00              |

|   | +5          | \$27000          | \$1c000            | \$b8000              |

|   | +4          | \$1f800          | \$16000            | \$af400              |

|   | +3          | \$17c00          | \$10400            | \$a5800              |

|   | +2          | \$10000          | \$ac00             | \$9a400              |

|   | +1          | \$800            | \$5400             | \$8e000              |

|   | 0           | 0                | 0                  | \$80000              |

|   | -1          | \$f7c00          | \$fac00            | \$80000              |

|   | -2          | \$efc00          | \$f5c00            | \$80000              |

|   | -3          | \$e8000          | \$f0c00            | \$80000              |

|   | -4          | \$e0400          | \$ec000            | \$80000              |

|   | <b>-</b> 5  | \$d8c00          | \$e7e00            | \$80000              |

|   | -6          | \$d1800          | \$e2800            | \$80000              |

|   | -7          | \$ca400          | \$de000            | \$80000              |

|   | -8          | \$c3c00          | \$d9800            | \$80000              |

|   | -9          | \$bd400          | \$d5000            | \$80000              |

|   | -10         | \$b7400          | \$d0400            | \$80000              |

|   | -11         | \$b1800          | \$cbc00            | \$80000              |

|   | -12         | \$ac400          | \$c6c00            | \$80000              |

|   | –13         | \$a7400          | \$c1800            | \$80000              |

|   | -14         | \$a2800          | \$bb400            | \$80000              |

|   | -15         | \$9e400          | \$b2c00            | \$80000              |

#### 3.5. Memory Area

# 3.5.1. Status Memory

The memory cells given in the following table should be accessed by the 'read control interface data' I<sup>2</sup>C command (see Section 3.3.2. on page 15) because only the 16 LSBs of these memory blocks are used. The memory area table is a consecutive memory block in the D0 memory that keeps all important status information that monitors the MPEG decoding process. The 'read control interface data' command resets the MPEG-FRAME-SYNC at *Pl4* as described in Section 2.7.4.

Table 3-9: Status Memory Area

| Address           | Offset <sup>1)</sup> | R/W | Name                  | Function                                |

|-------------------|----------------------|-----|-----------------------|-----------------------------------------|

| D0:\$300          | 0                    | r   | MPEGFrameCount        | counts the MPEG frames                  |

| D0:\$301          | 1                    | r   | MPEGStatus1           | MPEG header / status information        |

| D0:\$302          | 2                    | r   | MPEGStatus2           | MPEG header                             |

| D0:\$303          | 3                    | r   | CRCErrorCount         | counts CRC errors during MPEG decoding  |

| D0:\$304          | 4                    | r   | NumberOfAncillaryBits | number of bits in ancillary data        |

| D0:\$305<br>\$321 | 5                    | r   | AncillaryData         | organized in words a 16 bit (MSB first) |

<sup>1)</sup> Offset applies to the 'read control interface data' command

# 3.5.1.1. MPEG Frame Counter

| Address  | Offset | R/W | Name           | Function               |

|----------|--------|-----|----------------|------------------------|

| D0:\$300 | 0      | r   | MPEGFrameCount | counts the MPEG frames |

The counter will be incremented with each new frame that is decoded. With an invalid MPEG bit stream as its input (e.g. if an invalid header is detected), the

MAS 3507D resets the MPEGFrameCount cell to '0'. The MPEGFrameCount is also returned by the 'default read' command as described in Section 3.3.9.

# 3.5.1.2. MPEG Status 1

| Address  | Offset | R/W | Name        | Function                         |

|----------|--------|-----|-------------|----------------------------------|

| D0:\$301 | 1      | r   | MPEGStatus1 | MPEG header / status information |

The MPEGStatus1 contains the bits 15...11 of the MPEG header and some status bits. It will be set each frame, directly after the header has been decoded from the bit stream.

Table 3-10: MPEG Status 1

| Bits   | Name/Value               | Comment                          |

|--------|--------------------------|----------------------------------|

| 19, 15 | %xxxx.x                  | don't care                       |

| 14, 13 | MPEG ID                  | Bits 11, 12 of the MPEG-header   |

|        | %00<br>%01<br>%10<br>%11 | MPEG 2.5 reserved MPEG 2 MPEG 1  |

| 12, 11 | Layer                    | Bits 13, 14 of the MPEG-header   |

|        | %00<br>%01<br>%10<br>%11 | reserved Layer 3 Layer 2 Layer 1 |

| 10     | %1                       | not protected by CRC             |

| 92     |                          | private bits                     |

| 1      | %1                       | CRC Error                        |

| 0      | %1                       | invalid frame                    |

# 3.5.1.3. MPEG Status 2

| Address  | Offset | R/W | Name        | Function    |

|----------|--------|-----|-------------|-------------|

| D0:\$302 | 2      | r   | MPEGStatus2 | MPEG header |

The MPEGStatus2 contains the 16 LSBs of the MPEG header. It will be set directly after synchronizing to the bit stream.

Table 3-11: MPEG Status 2

| Bits   | Value/Name                                                                                                        | Comment                                                                        |                                                                 |                                                                                                          |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| 19, 16 |                                                                                                                   | don't care                                                                     |                                                                 |                                                                                                          |  |  |  |  |

| 1512   | Bit rate index                                                                                                    | MPEG 1<br>(Layer 2)<br>in kbit/s                                               | MPEG 1<br>(Layer 3)<br>in kbit/s                                | MPEG 2 in kbit/s<br>(Layer 2 & 3)<br>MPEG 2.5 in kbit/s                                                  |  |  |  |  |

|        | %0000<br>%0001<br>%0010<br>%0011<br>%0100<br>%0101<br>%0111<br>%1000<br>%1001<br>%1010<br>%1011<br>%1100<br>%1111 | free 32 48 56 64 80 96 112 128 160 192 224 256 320 384 forbidden               | free 32 40 48 56 64 80 96 112 128 160 192 224 256 320 forbidden | free<br>8<br>16<br>24<br>32<br>40<br>48<br>56<br>64<br>80<br>96<br>112<br>128<br>144<br>160<br>forbidden |  |  |  |  |

| 11, 10 | %00<br>%01                                                                                                        | MPEG 1<br>44.1 kHz<br>48 kHz                                                   | MPEG 2<br>22.05 kHz<br>24 kHz                                   | MPEG 2.5<br>11.025 kHz<br>12 kHz                                                                         |  |  |  |  |

|        | %10<br>%11                                                                                                        | 32 kHz<br>reserved                                                             | 16 kHz<br>reserved                                              | 8 kHz<br>reserved                                                                                        |  |  |  |  |

| 9      | Padding bit                                                                                                       |                                                                                |                                                                 |                                                                                                          |  |  |  |  |

| 8      | Private bit                                                                                                       |                                                                                |                                                                 |                                                                                                          |  |  |  |  |

| 7, 6   | Mode                                                                                                              |                                                                                |                                                                 |                                                                                                          |  |  |  |  |

|        | %00<br>%01<br>%10<br>%11                                                                                          | stereo joint_stereo (intensity stereo / ms_stereo) dual channel single_channel |                                                                 |                                                                                                          |  |  |  |  |

| 5, 4   | Mode extension<br>(if joint stereo only)                                                                          | intensity stereo                                                               | ms_stereo                                                       |                                                                                                          |  |  |  |  |

|        | %00<br>%01<br>%10<br>%11                                                                                          | off<br>on<br>off<br>on                                                         | off<br>off<br>on<br>on                                          |                                                                                                          |  |  |  |  |

| 3      | %0 / 1                                                                                                            | copyright not protected                                                        | / copyright protected                                           |                                                                                                          |  |  |  |  |

| 2      | %0 / 1                                                                                                            | copy / original                                                                |                                                                 |                                                                                                          |  |  |  |  |

| 1, 0   | Emphasis                                                                                                          | indicates the type of emphasis                                                 |                                                                 |                                                                                                          |  |  |  |  |

|        | %00<br>%01<br>%10<br>%11                                                                                          | none<br>50/15 μs<br>reserved<br>CCITT J.17                                     |                                                                 |                                                                                                          |  |  |  |  |

#### 3.5.1.4. CRC Error Counter

| Address  | Offset | R/W | Name          | Function                               |

|----------|--------|-----|---------------|----------------------------------------|

| D0:\$303 | 3      | r   | CRCErrorCount | counts CRC errors during MPEG decoding |

The counter will be increased by each CRC error in the MPEG bit stream. It will not be reset by losing the synchronization.

#### 3.5.1.5. Number Of Ancillary Bits

| Address  | Offset | R/W | Name                  | Function                         |

|----------|--------|-----|-----------------------|----------------------------------|

| D0:\$304 | 4      | r   | NumberOfAncillaryBits | number of bits in ancillary data |

This cell displays the number of valid ancillary bits stored beginning at D0:\$305.

# 3.5.1.6. Ancillary Data

| Address  | Offset | R/W | Name          | Function                                |

|----------|--------|-----|---------------|-----------------------------------------|

| D0:\$305 | 5      | r   | AncillaryData | organized in words a 16 bit (MSB first) |

| D0:\$321 |        |     |               |                                         |

This memory field contains the ancillary data. It is organized in words 16 bit each. The last ancillary bit transmitted in a frame is placed at bit 0 in D0:\$305. The position of the first ancillary data bit is locatable via the content of NumberOfAncillaryBits.

An example: 17 bits ancillary data in a frame:

A possible 'read ancillary data' algorithm would read the NumberOfAncillaryBits and the complete ancillary data area using the telegram:

```

<$3a><$68><$31><$1e> (offset=4, n=30)

<$3a><$69><$3b><receive 30 16-bit words>

```

For reducing the I<sup>2</sup>C protocol transfer traffic, it may be useful to split up the 'read ancillary data' algorithm into a first part that reads NumberOfAncillaryBits and a second that reads only NumberOfAncillaryBits/16+1 words.

MAS 3507D PRELIMINARY DATA SHEET

### Table 3-12: Ancillary data bit assignment

| D0: \$305      | 15 MSB | 14    | 13    | 12    | 11    | 10    | 09    | 08    | 07    | 06     | 05     | 04     | 03     | 02     | 01     | 00 LSB |

|----------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|--------|

| ancillary data | bit 1  | bit 2 | bit 3 | bit 4 | bit 5 | bit 6 | bit 7 | bit 8 | bit 9 | bit 10 | bit 11 | bit 12 | bit 13 | bit 14 | bit 15 | bit 16 |

Table 3-13: Ancillary data bit assignment

| D0: \$306      | 15 MSB | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 LSB |

|----------------|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| ancillary data | х      | х  | х  | x  | x  | х  | x  | х  | х  | x  | x  | x  | x  | x  | х  | bit 0  |

# 3.5.2. Configuration Memory

The configuration memory allows the controller advanced configuration possibilities, e.g. changing setups for the crystal frequency or changing the digital format of the serial audio output data interface.

Table 3–14: Configuration memory area<sup>1)</sup>

| Address  | R/W | Name         | Function                                                                                          |         |

|----------|-----|--------------|---------------------------------------------------------------------------------------------------|---------|

| D0:\$32d | r/w | PLLOffset48  | PLL offset (if f <sub>s</sub> = 48, 24, 12, 32, 16, or 8 kHz), validate by 'run \$fcb' command    |         |

| D0:\$32e | r/w | PLLOffset44  | PLL offset (if f <sub>s</sub> = 44.1, 22.05, 11.025 kHz), validate by ' <i>run</i> \$fcb' command |         |

| D0:\$32f | r/w | OutputConfig | Configuration of the I <sup>2</sup> S audio output interface validate by 'run \$fcb' command      |         |

| D1:\$7f8 | r/w | LL           | Left → Left Gain                                                                                  |         |

| D1:\$7f9 | r/w | LR           | Left → Right Gain                                                                                 | 0       |

| D1:\$7fa | r/w | RL           | Right → Left Gain                                                                                 | 0       |

| D1:\$7fb | r/w | RR           | Right → Right Gain                                                                                | \$80000 |

<sup>1)</sup> **Important note:** Writing into undocumented memory cells is always possible, but it is highly recommended not to do so. It may damage the function of the firmware and may even lead to a complete system crash of the decoder operation which can only be restored by a reset.

| Address  | R/W | Name        | Name Function                                                                                      |  |

|----------|-----|-------------|----------------------------------------------------------------------------------------------------|--|

| D0:\$32d | r/w | PLLOffset48 | PLL offset (if f <sub>s</sub> = 48, 24, 12, 32, 16, or 8 kHz), validate by 'run \$fcb' command     |  |

| D0:\$32e | r/w | PLLOffset44 | PLL offset (if f <sub>s</sub> = 44.1, 22.05, 11.025 kHz), validate by ' <i>run \$fcb</i> ' command |  |

With these memory cells it is possible to choose other frequencies than the standard *CLKI* frequencies. Please note:

- PLLOffset48 is valid for f<sub>s</sub> = 48, 24, 12, 32, 16, or 8 kHz.

- PLLOffset44 is valid for f<sub>s</sub> = 44.1, 22.05, 11.025 kHz.

Table 3–15 shows the default values which will be set by the firmware according to the start-up configuration.

Table 3-15: PLLOffset48 and PLLOffset44

| f <sub>CLKI</sub> | PLLOffset48 | PLLOffset44 |

|-------------------|-------------|-------------|

| 14.725 MHz        | 0.351986    | -0.732862   |

| 14.5792 MHz       | 0.473684    | -0.621052   |

It is also possible to run the MAS 3507D with other clocks. In broadcast mode, it is necessary to adjust the PLLOffsets to this clock, otherwise it will not lock to the MPEG bit stream. In multimedia mode, it is recommended to adjust the PLLOffsets to the crystal, otherwise it would result in a frequency shift (music will be played faster or slower). For adjusting, the following procedure must be done:

- Calculate the PLLOffsets according to:

$$f_{CLKI} = \frac{24,576 \cdot 8}{13 + PLLOffset48} = \frac{22,5792 \cdot 8}{13 + PLLOffset44}$$

with -0.74 < PLLOffset < 0.74. This corresponds to a frequency range of 14.31...14.73 MHz for the crystal, if both 44.1 kHz and 48 kHz based sample frequencies are used. The range is extended in an application with a fixed sampling frequency, as Table 3–16 shows.

- Write the PLLOffsets to the memory (PLLOffset48 D0:\$32d, PLLOffset44 D0:\$32e).

- Send a 'run \$fcb' command. With the jump to this address, the settings in the memory will be valid for the internal processing.

Table 3-16: f<sub>Clk1</sub> for max./ min. PLLOffsets

| PLLOffset | f <sub>CLKI</sub> for f <sub>s</sub><br>related to 48 kHz | f <sub>CLKI</sub> for f <sub>s</sub> related<br>to 44.1 kHz |

|-----------|-----------------------------------------------------------|-------------------------------------------------------------|

| -0.74     | 16.0365 MHz                                               | 14.7336 MHz                                                 |

| 0.74      | 14.309 MHz                                                | 13.1465 MHz                                                 |

#### Example:

A very common crystal frequency is 14.31818 MHz (NTSC color subcarrier). The

$$PLLOffset48 = \frac{24,576 \cdot 8}{14,31818} - 13 = 0,7314$$

and

$$PLLOffset44 = \frac{22,5792 \cdot 8}{14,31818} - 13 = -0,3843$$

are inside the range -0.74 ... 0.74.

MAS 3507D PRELIMINARY DATA SHEET

# 3.5.2.2. Output Configuration

| Address  | R/W | Name         | Function                                                                                     | Default |

|----------|-----|--------------|----------------------------------------------------------------------------------------------|---------|

| D0:\$32f | r/w | OutputConfig | Configuration of the I <sup>2</sup> S audio output interface validate by 'run \$fcb' command |         |

The content of this memory cell depends on the startup configuration and will be set by the firmware. Nevertheless, the audio output interface is configurable by the software to work in different 16 bit/sample modes and 32 bit/sample modes (see Section 2.7.2. on page 10). For adjusting to this, the following procedure has to be done:

- Choose the output mode (see Table 3-17).

- Write this value to the memory (D0:\$32f).